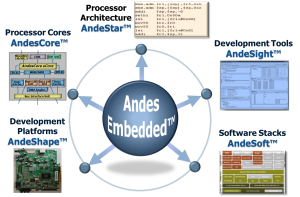

“Our newest products, N25 32bit and NX25 64bit RISC-V based cores coupled with a mature toolchain, will provide even more value to customers in these advanced nodes by providing both high speed and power efficiency,” says Andes CTO Charlie Su.

Andes announced it was supporting RISC-V open-source architecture in May 2017.

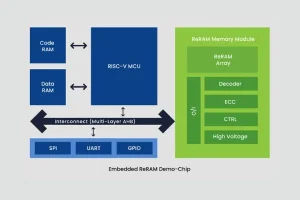

The Andes ISA, called AndeStar V5, supports 64-bits and RISC-V as a subset and will bring the open, compact, and modular RISC-V into mainstream SoC applications.

The AndesCore NX25 in a typical configuration will deliver a clock frequency of over 1GHz with area of only 67K gates and with power consumption as little as 17 µW/MHz in a TSMC 28nm process.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News