Intels Xeon-Prozessorfamilie Skylake-SP läuft vom Stapel: Erste Benchmark-Ergebnisse gegen AMD Epyc

Die skaliberbaren Xeons gibt es alle im gleichen Pinout für 2 bis 8 Sockel. Die neuen Prozessoren enthalten bis zu 28 Kerne, bieten AVX512 und unterteilen sich in die Linien Platin, Gold, Silber und Bronze.

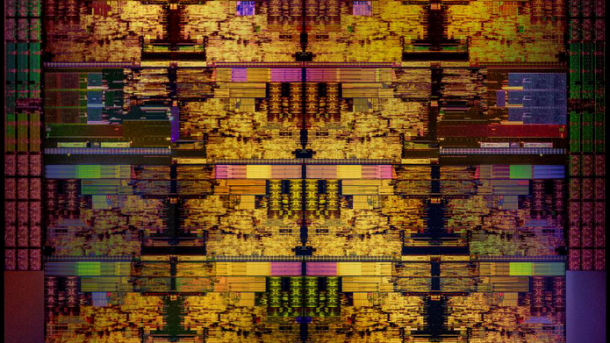

Skylake-SP mit 28 Kernen: Die Shot

(Bild: Intel)

Es hat ein paar Monate länger gedauert als ursprünglich geplant, doch nun ist Intels skalierbare Xeon-Familie (Skylake-SP) offiziell vom Stapel gelaufen – mit bis zu 28 Kernen und mit einer auf 512 Bit und 32 Register erweiterten Vektoreinheit AVX512. Im Schnitt soll das neue 28-kernige Flaggschiff Xeon Platinum 8180 um 65 Prozent schneller sein als der Vorgänger Broadwell EP (Xeon E5-2699Av4) beziehungsweise um 50 Prozent bei vier Sockeln (Xeon E7-8890v4). Der Linpack-Benchmark explodiert natürlich dank der verdoppelten Breite der Vektoreinheiten um mehr als den Faktor 2.

(Bild: Intel)

Aber wahrscheinlich muss man dafür auch deutlich mehr bezahlen – Preise hatte Intel in dem vorab in Hillsboro/Oregon abgehaltenen Presse-Workshop nicht bekannt gegeben. Hinzu kommt, dass es die Trennung in Xeon E5 und E7 mit unterschiedlichen Sockeln in Zukunft nicht mehr geben wird, dafür die vier Klassen Platin, Gold, Silber und Bronze – alle für den Sockel P3 mit 3647 Pins. Wer etwa 28 Kerne für ein Zweisockelsystem haben möchte, muss dann kräftig in die Tasche greifen, denn den gibt’s nur als Platinum 8180. Alle Platin-Chips sind für bis zu acht Sockel "zugelassen", die Gold-Chips dürfen nur für vier und die Silber und Bronze nur für zwei. "Blech" für Singlesocket-Systeme gibt es derzeit nur in Gestalt des Skylake X, für Xeons kommts vielleicht noch.

Die niedrigeren Edelmetall-Kategorien müssen neben einer niedrigeren Kernzahl, kleinerem L3-Cache und weniger Sockeln noch einige weitere Herabstufungen in Kauf nehmen, etwa beim unterstützten Speicher und der Zahl und Geschwindigkeit der UPI-Links (siehe Tabelle) sowie bei der Qualität von AVX512. Denn je nach Kaste gibt es eine oder zwei AVX512-FMA-Pipelines. Gold ist dafür nochmal in "Obergold" (61xx) und "Untergold(51xx) aufgeteilt. Nur Platin und Obergold besitzen zwei FMAs, alle anderen lediglich eine, damit kommen sie im Linpack-Benchmark bei gleicher Kernzahl nur etwa auf die Hälfte.

| Kategorien | |||

| Edelmetall | Sockel | AVX512-FMA | Speicher |

| Platinum | 2,4,8 | 2 | DDR4-2666 |

| Gold (61XX) | 2,4 | 2 | DDR4-2666 |

| Gold (51XX) | 2,4 | 1 | DDR4-2400 |

| Silver | 2 | 1 | DDR4-2400 |

Der L3-Cache ist in Segmente von jeweils 1,375 MByte aufgeteilt, die direkt an den Prozessorkernen sitzen. Manche SKUs mit kleinerer Kernzahl dürfen aber auch die L3-Segmente von abgeschalteten Kernen mitbenutzen. Der L2-Cache wurde gegenüber der Desktop-Version vervierfacht und ist jetzt 16-fach assoziativ. Er braucht jetzt beim Zugriff zwar zwei Takte Latenz mehr, aber die Vervierfachung der Kapazität gleicht das weit mehr als aus.

Mesh statt Ringbus

Neu ist ferner, wie die Kerne, die L3-Cache-Segmente, die nunmehr sechs Speichercontroller und die I/O-Interfaces für UPI (der Nachfolger von QPI) sowie PCIe 3 miteinander kommunizieren. Keine Ringbusse mehr, sondern ein Mesh, ähnlich wie beim Xeon Phi. Dabei haben die vertikalen und horizontalen Verbindungen unterschiedliche Laufzeiten, ein (Uncore-)Takt hier, drei da. Im Worst Case, wenn der Kern ganz links unten mit dem PCIe-Controller ganz rechts oben kommuniziert, kommen 20 Takte zusammen. Smarte Treiberprogrammierer werden vielleicht die Lage der Kerne im Chip heraustüfteln und so den bestgelegenen Kern auswählen. Ähnlich wie bei den Ringsystemen zuvor mit CoD (Cluster on Die) kann man aber auch das Mesh in zwei Teile aufspalten, die dann als zwei NUMA-Knoten mit je drei Speichercontrollern angesprochen werden. Bei guter NUMA-Programmierung kann man dann ein paar zusätzliche Prozent an Performance herauskitzeln.

(Bild: Intel)

AVX512-Spielarten

AVX512 ist nicht gleich AVX512: es gibt hier verschiedene Spielarten, so dass die Befehlssätze vom Xeon Phi Knights Landing und die vom Skylake-SP nicht völlig identisch sind. So kennt der Xeon Phi trigonometrische und reziproke AVX512-Instruktionen (AVX512ER) – die bietet der Skylake-SP nicht, hat dafür aber Byte- und Word-Instruktionen (AVX512BW) und kann auch die alten AVX-und SSE-Einheiten auf 32 Register "aufblasen" (AVX512VL)

Neu ist auch, dass es je nach den verwendeten Instruktionen drei verschiedene Takte gibt. Dabei unterscheidet Intel zudem noch zwischen "heavy",– mit FP-oder Int-Multiplikationen – und "light" ohne diese. Bei AVX512 wird nur bei heavy auf einen noch niedrigeren Takt geschaltet. Bei AVX2 muss dafür bei Light-Nutzung der Takt nicht abgesenkt werden. Früher gab es ausführliche Tabellen über die AVX- und Non-AVX-Takte und Turbo-Bins aller SKUs. Aber für den Skylake-SP hüllt sich Intel diesbezüglich bislang noch in Schweigen.

Interessant ist auch, wie Intel den Desktop-Skylake-Kern für die Serverchips erweitert hat. Die beiden dort vorhandenen 256-bittigen AVX2-Einheiten werden zu einer 512-bittigen zusammengeschaltet. Eine zweite 512-Bittige wird außen angekoppelt. Unterschiedliche Latenzen sollen die beiden AVX512-Einheiten aber dennoch nicht haben.

Testergebnisse: Skylake-SP vs. AMD Epyc

Ein Testsystem mit zweimal Xeon Platinum 8180 ackert derzeit im c't-Labor. Hier geben wir vorab ein paar erste, vorläufige Ergebnisse mit den "Klassikern" SPEC CPU2006, Stream und Linpack.

Intel hat vorab im Workshop einige Werte bei allerbester Optimierung mit dem Intel-Compiler bekannt gegeben -- ein paar Kurzläufer wie CineBench und Linpack konnte man dort auch selbst messen. Zum Launch könnten noch bessere Ergebnisse bekannt gegeben werden. Für SPEC CPU2006 auf dem Zweisockelsystem erzielte das Platinum-8180-System 2550 SPECint_rate_2006base und 1720 SPECfp_rate_2006base. AMDs Epyc-7601, gemessen mit dem alten, nicht für Zen optimierten Open64-Compiler liegt mit 2100/1660 nicht all zu viel darunter. Der wird sich vermutlich ohnehin nicht so sehr mit Intels Flaggschiff als vielmehr mit dem Gold-6148 duellieren müssen, mit dem er dann in etwa auf Augenhöhe liegen dürfte.

(Bild: Intel)

Angeregt durch AMD haben wir zunächst einmal die CPU2006-Suite nur mit gcc/g++ -m64- -O2 (gcc6.4) laufen lassen – das was in der Linux-Welt sicherlich bei Weitem am häufigsten verwendet wird. Und da liegt Epyc sogar mit Intels Flaggschiff in etwa auf Augenhöhe: 1380 SPECint_rate_base2006 für das Platinum 8180-System, 1300 für Epyc 7601. Bei SPECfp_rate warf der gcc auf dem Xeon Platinum 8180 eine bislang noch ungeklärte Floatingpoint Exception bei einem der Benchmarks (416.gamess). Die restlichen 16 Benchmarks ergeben eine geschätzten Wert von nur 960 SPECfp_rate_base2006 est. während das Epyc-7601-System dank seiner weit besseren Speicherperformance auf 1220 kommt.

Für den Speicherbenchmark Stream hat Intel 199 GFlops angegeben – wir kamen bislang auf 187, aber da kann man noch optimieren – etwa die bestgelegenen Kerne auswählen. AMDs Epyc ist in dieser Disziplin mit seinen 8 Speicherkanälen klar im Vorteil, er liegt erwartungsgemäß etwa um ein Drittel besser – nach AMDs Messungen bei 247 GFlops, wir hatten mit unserem Stream-5.10-Code, mit Icc16 kompiliert, sogar 260 GFlops gemessen.

Bei Linpack ist AMDs Epyc mangels AVX512 natürlich deutlich im Nachteil, kommt mit einer speziellen MPI-Version nur auf 1050 GFlops. Auch Intel verwendet eine MPI-Version und erzielt bei 120.000 Gleichungen auf obigem System 3296 GFlops. Wir bleiben traditionsgemäß bei der OpenMP-Fassung, die früher mal schnellere, inzwischen aber zumeist etwas langsamere Werte liefert. Bisheriger Zwischenstand im c't-Labor ist 2690 GFlops[ --] aber da kann man noch mit Page-Locking, Transparenten Hugepages, Numactl und so weiter spielen und vor allem auch noch das Mesh in zwei Knoten (SNC2) aufteilen – da ist also noch einiges mehr drin.

Das Flops-Programm von Alex Yee, das mal den Ryzen-FMA-Bug aufdeckte, liefert die absolute Obergrenze. Es kommt bei "Double-Precision - 512-bit AVX512" auf 4096 GFlops – das entspricht etwa 2,3 GHz bei 32 Flops/Takt.

CineBench haben wir beim Presseworkshop in den USA gemessen: Mit 6580 für ein Platinum-8180-System nicht schlecht – aber ähnliche Werte konnten wir auch mit AMDs Epyc 7601 messen, AMD selbst kam später dann sogar auf nahezu 6900.

Mit vier (oder gar acht) Sockeln kann AMD allerdings gar nicht aufwarten, da bleibt Intel voraussichtlich für längere Zeit alleine: SPECint/fp von 4920//3320, und ein Linpack von 5777 GFlops, das sind schon beeindruckende Werte. – Auf dem Presseworkshop war man gar noch einen Tick schneller und kam live auf 5919 GFlops.

Mehr Benchmark-Ergebnisse und Architekturdetails folgen in den nächsten c't-Ausgaben .

| Die Xeon-Scalable-Familie | ||||||

| Prozessor |

"Edelmetall" |

Kerne | Basistakt | L3-Cache | TDP | OEM-Preis |

| Optimiert für größte Performance/Kern | ||||||

| 8180(M) | Platinum | 28 | 2,5 GHz | 38,5M | 205W | |

| 8168 | Platinum | 24 | 2,7 GHz | 33M | 205W | |

| 8158 | Platinum | 12 | 3,0 GHz | 24,75M | 150W | |

| 8156 | Platinum | 4 | 3,6 GHz | 16,5M | 105W | |

| 6148(F) | Gold | 20 | 2,4 GHz | 27,5M | 150W | |

| 6154 | Gold | 18 | 3,0 GHz | 24,75M | 200W | |

| 6150 | Gold | 18 | 2,7 GHz | 24,75M | 165W | |

| 6142 (F)(M) | Gold | 16 | 2,6 GHz | 22M | 150W | |

| 6132 | Gold | 14 | 2,6 GHz | 19,25M | 140W | |

| 6146 | Gold | 12 | 3,2 GHz | 24,75M | 165W | |

| 6136 | Gold | 12 | 3,0 GHz | 24,75M | 150W | |

| 6126(F) | Gold | 12 | 2,6 GHz | 19,25M | 125W | |

| 6144 | Gold | 8 | 3,5 GHz | 24,75M | 150W | |

| 6134(M) | Gold | 8 | 3,3 GHz | 24,75M | 130W | |

| 6128 | Gold | 6 | 3,4 GHz | 19,25M | 115W | |

| 5122 | Gold | 4 | 3,6 GHz | 16,5M | 105W | |

| Optimiert für balancierte Energieeffizienz | ||||||

| 8176(F)(M) | 28 | 2,1 GHz | 38,5M | 165W | ||

| 8170 | Platinum | 26 | 2,1 GHz | 35,75M | 165W | |

| 8146 | Platinum | 26 | 2,0 GHz | 35,75M | 150W | |

| 8160(F) | Platinum | 24 | 2,1 GHz | 33M | 150W | |

| 8153 | Platinum | 16 | 2,0 GHz | 22M | 125W | |

| 6152 | Gold | 22 | 2,1 GHz | 30,25M | 140W | |

| 6138(F) | Gold | 20 | 2,0 GHz | 27,5M | 125W | |

| 6140 | Gold | 18 | 2,3 GHz | 24,75M | 140W | |

| 6130(F) | Gold | 16 | 2,1 GHz | 22M | 125W | |

| 5120 | Gold | 14 | 2,2 GHz | 19,25M | 105W | |

| 5118 | Gold | 12 | 2,3GHz | 16,5M | 105W | |

| 5115 | Gold | 10 | 2,4 GHz | 13,75M | 85W | |

| 4116 | Silber | 12 | 2,1 GHz | n.n | 85W | |

| 4144 | Silber | 10 | 2,2 GHz | n.n | 85W | |

| 4112 | Silber | 4 | 2,6 GHz | n.n | 85W | |

| 4110 | Silber | 8 | 2,1 GHz | n.n | 85W | |

| 4108 | Silber | 8 | 1,8 GHz | n.n | 85W | |

| 3106 | Bronze | 8 | 1,7 GHz | n.n | 85W | |

| 3104 | Bronze | 6 | 1,7 GHz | n.n | 85W | |

| F:mit integriertem Omni-Path-Fabric (+ ca. 10 W), M:auf 1,5 TByte/Sockel erweiterte Speicherkapazität | ||||||

Skylake-SP Architektur-Deep-Dive: Originalfolien von Intel

Intel Skylake-SP: Architektur-Deep-Dive (72 Bilder)

(as)