MIPSfpga+ / mipsfpga-plus / MFP is a cleaned-up and improved variant of MIPSfpga-based system defined in MIPSfpga Getting Started package (MFGS). The new features include:

- The ability to load a software program using ubiquitous $5 FTDI-based USB-to-UART connector instead of $50 Bus Blaster that is difficult to get in some places of the globe

- The ability to change the clock frequency on the fly from 50 or 25 MHz down to 1 Hz (one cycle a second) to observe the work of CPU in real time, including cache misses and pipeline forwarding

- An example of integration of a light sensor with SPI protocol

- Smaller software initialization sequence that fits in 1 KB instead of 32 KB memory, which allows porting MIPSfpga to a wider selection of FPGA boards, without using external memory

- Miscellaneous fixes like improving AHB-Lite slave to handle narrow uncached writes of sizes 1 or 2-bytes

- Easy to use configurable SDRAM interface module

- Altera MAX10 ADC interface module support

- Widely used UART16550 interface module

- External interrupt controller that is working throw MIPS microAptiv core Interrupt Interface

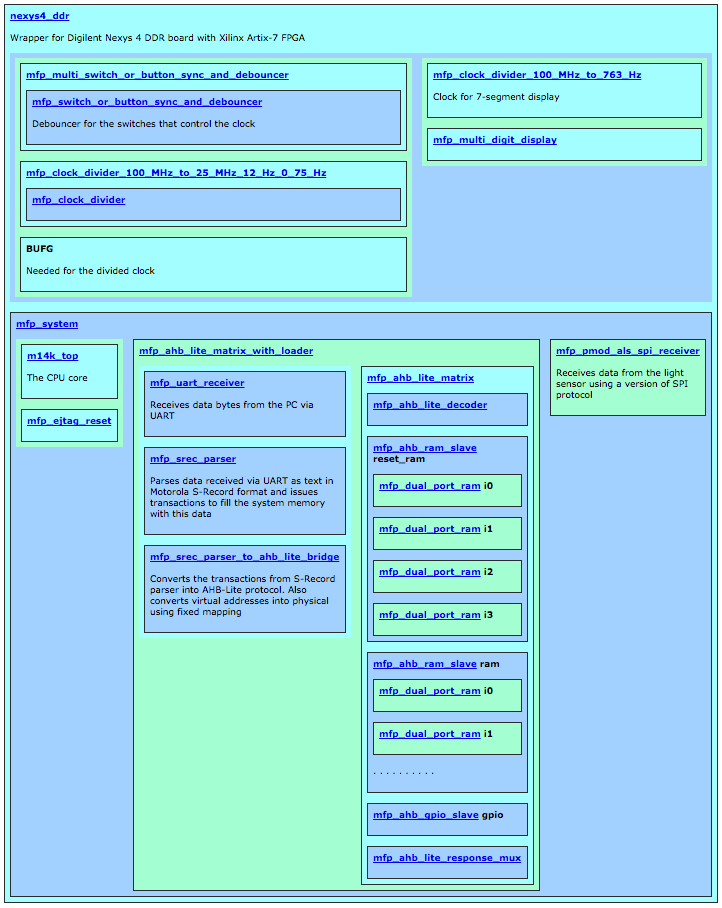

The hierarchy of synthesizable modules for Digilent Nexys 4 DDR with Xilinx Artix-7 FPGA:

MIPSfpga+ currently works on these FPGA boards:

- Digilent Nexys 4 DDR board with Xilinx Artix-7 FPGA. See the Appendix A about how the board is connected with the applicable peripherals.

- Digilent Nexys 4 board with Xilinx Artix-7 FPGA (no DDR, soon to be discontinued).

- Digilent Basys 3 with Xilinx Artix-7.

- Terasic DE0-CV with Altera Cyclone V. See the Appendix B about how the board is connected with the applicable peripherals.

- Terasic DE2-115 with Altera Cyclone IV

- Terasic DE0-Nano board with Altera Cyclone IV FPGA.

- Terasic DE0 with Altera Cyclone III

- Terasic DE1 with Altera Cyclone II

- Terasic DE10-Lite with Altera MAX10

- Terasic DE10-Nano with Altera Cyclone V

There are three planned ports:

- Marsohod 3 board with Altera MAX10 FPGA

- Digilent Arty with Xilinx Artix-7. MIPSfpga+ is likely to work on this board with no modification except adding the board wrapper (top-level Verilog and pin constraints).

- Terasic DE2 with Altera Cyclone II

The source code for MIPSfpga+ is located at http://github.com/MIPSfpga/mipsfpga-plus; this code does not include any source code of MIPS microAptiv UP CPU core from MIPSfpga Getting Started package. A user of MIPSfpga+ is supposed to download Getting Started package from Imagination Technologies web site: MIPSfpga Getting Started Guide 2.0 or MIPSfpga Getting Started Guide 1.3.

After downloading both MIPSfpga from Imagination site and MIPSfpga+ from GitHub, the user is expected to install MIPSfpga under 64-bit Microsoft Windows (either Windows 7 or Windows 8) by placing MIPSfpga core source files to MIPSfpga+\core directory. To do this one need to copy to MIPSfpga+\core all the files from 'MIPSfpga_GSG_1.3\MIPSfpga\rtl_up' when using MIPSfpga 1.3 or from 'MIPSfpga_GSG_v2.0\MIPSfpga_GSG\rtl_up\core' in the case of using MIPSfpga 2.0. The paths inside MIPSfpga+ synthesis and simulation scripts rely on such installation.

MIPSfpga+ (as well as the original MFGS package) can be also used on a workstation with 32-bit Windows, 32-bit Linux, 64-bit Linux, with or without Windows or Linux virtual machine. It is possible to install MIPSfpga+ in different directories, and use it with a number of Verilog simulators and synthesis tools: Synopsys VCS, Cadence IES, Mentor ModelSim, Icarus Verilog with GTKWave, Xilinx ISim and Vivado, Altera Quartus II, Synopsys Synplify Pro and others. Some usage scenarios require modifying the scripts and adhering to specific versions of EDA and software development tools, for example:

- In order to use MIPSfpga or MIPSfpga+ on a workstation with 32-bit Windows, it is necessary to use Mentor Sourcery CodeBench Lite Edition for MIPS ELF instead of Imagination Codescape MIPS SDK Essentials. This requires some minimal modifications of certain scripts (changing the program name prefixes).

- In order to use MIPSfpga or MIPSfpga+ with Altera FPGAs on a workstation with 32-bit Windows or 32-Linux, it is necessary to use Altera Quartus II Web Edition version 13.1 instead of the latest version 15.1 that does not work on workstations with 32-bit operating systems.

How to synthesize mipsfpga-plus for Terasic DE0-CV board:

- Unzip MIPSfpga 2.0 Getting Started Guide to C:\MIPSfpga

- Get mipsfpgfa-plus into C:\github\mipsfpga-plus

- copy all the files from C:\MIPSfpga\MIPSfpga_GSG\rtl_up\core to C:\github\mipsfpga-plus\core

- cd C:\github\mipsfpga-plus\boards\de0_cv

- make_project.bat

- Run Altera Quartus II

- Open project C:\github\mipsfpga-plus\boards\de0_cv\project\de0_cv.qpf

- Analyze/Synthesize/Place&Route/Assemble

- Open Device / Hardware Setup / ByteBlaster / Set file / ouput_files / de0_cv.sof / Start

How to load a software example into mipsfpga-plus using BusBlaster and OpenOCD:

cd C:\github\mipsfpga-plus\programs\00_counter 02_compile_and_link.bat 11_upload_to_the_board.bat

How to load a software example into mipsfpga-plus using USB-to-UART-based serial loader:

cd C:\github\mipsfpga-plus\programs\00_counter 02_compile_and_link.bat 08_generate_motorola_s_record_file.bat 09_check_which_com_port_is_used.bat

Modify 10_upload_to_the_board_using_uart.bat.

10_upload_to_the_board_using_uart.bat

Some details about scripts using: programs/README.md